Case-based Learning Approach to Teach Students How to Read Academic Papers

> **Peter Jamieson** Miami University

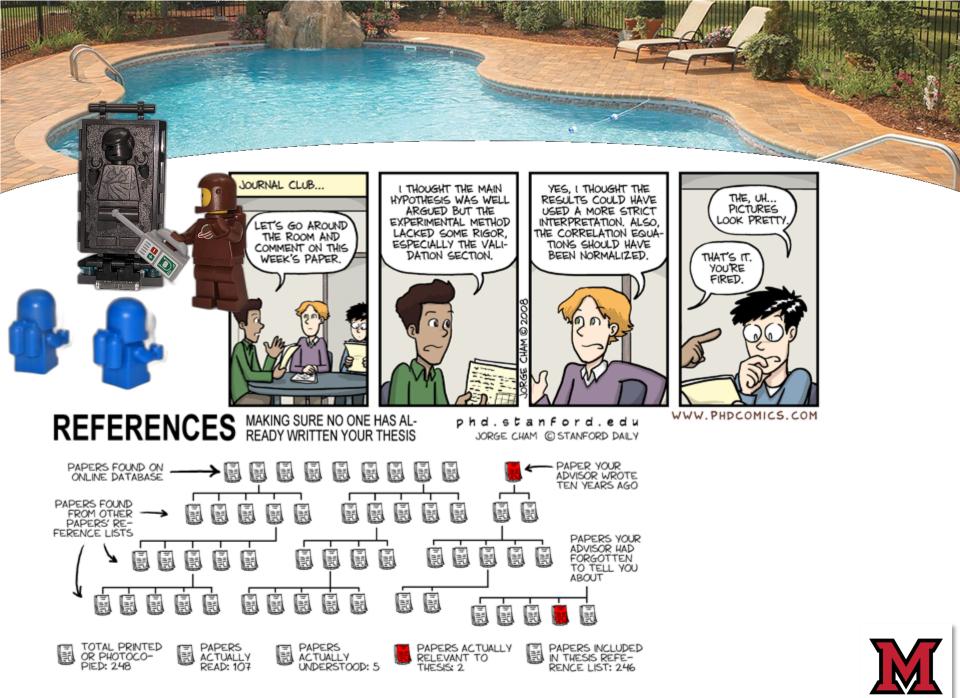

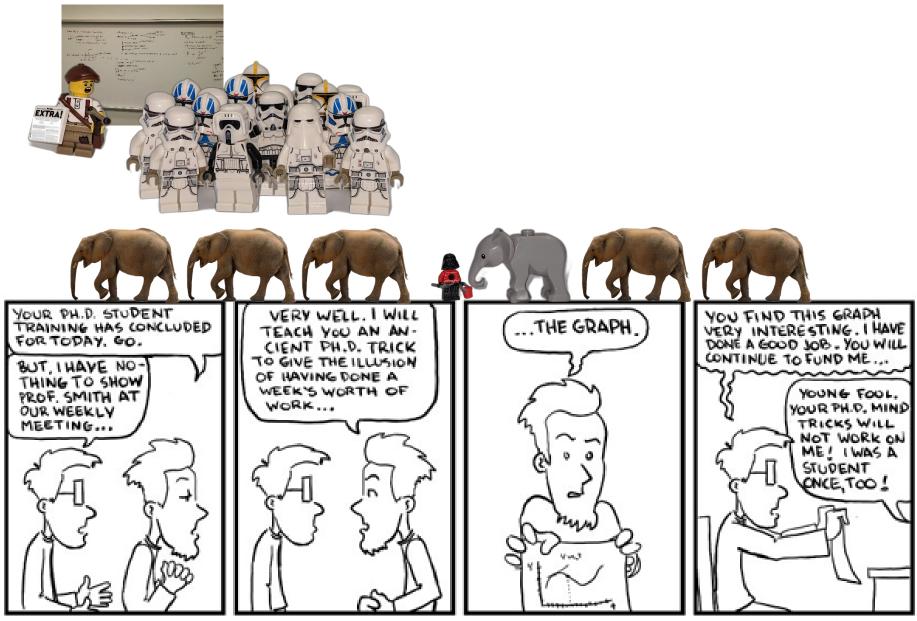

WWW. PHDCOMICS. COM

## THE AUTHOR LIST: GIVING CREDIT WHERE CREDIT IS DUE

The first author Senior grad student on the project. Made the figures.

81

0

The third author First year student who actually did the experiments, performed the analysis and wrote the whole paper. Thinks being third author is "fair". The second-to-last author Ambitious assistant professor or post-doc who instigated the paper.

## Michaels, C., Lee, E. F., Sap, P. S., Nichols, S. T., Oliveira, L., Smith, B. S.

The second author Grad student in the lab that has nothing to do with this project, but was included because he/she hung around the group meetings (usually for the food).

The middle authors Author names nobody really reads. Reserved for undergrads and technical staff.

= n

D

The last author The head honcho. Hasn't even read the paper but, hey, he got the funding, and his famous name will get the paper accepted.

0

0

**Y**TTT

00

## www.phdcomics.com

$\odot$

**ବ୍ଦ**

0

00

# New Approach

## The CASE STUDY HANDBOOK

How to Read, Discuss, and Write Persuasively About Cases

### WILLIAM ELLET

David Rosenthal . Lew G. Brown

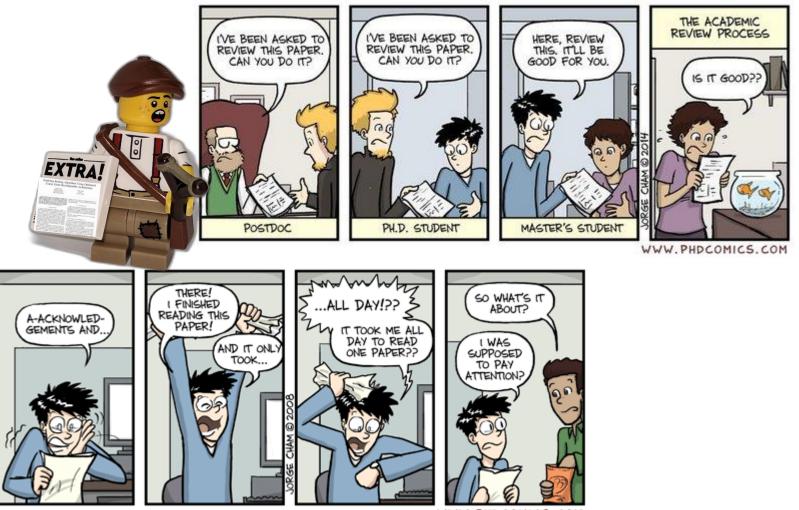

- 1) Case learners prepare for the case by reading and analyzing it

- 2) Optionally students can perform a deeper preparation by having a priori small group discussions

- 3) An in-class discussion is done for the case

- 4) An end-of-class summary is provided by the facilitator

# WIP - A Modification to the Case Study Method to Teach Students to Read Academic Papers

### Peter Jamieson 1) Case learners prepare for the <u>PAPER</u> by Miani University anari, yiZ4: 1208 Email: jamiespa@miamioh.edu reading and

then entering a safe learner space in which all the students Abstract-Most learners are introduced to academic papers discuss the case/paper. The instructor picks the cases/papers in their graduate work. Typically, most of us learn to read and understand these papers by reading many of them and listening to discuss and divine leave, the instruct r doc ments the scus Situation of the partition, Will us as liscus area of the the learners when needed. more serZr) ollea As at Dar e Care remain and the r the e we become better at this skill. There is a need to read papers in a particul PAPER or pranding Canada papers in a been do PAPER of pranding Canada papers in a been do PAPER of pranding Canada papers in a concerning the concerning of the skill. There is a need to read papers in a particul PAPER of pranding canada papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read papers in a concerning of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There is a need to read paper of the skill. There

We describe a work-in-progress to help teach students to read academic papers and build a base understanding of a field under the broad framework of case studies adopted and developed by business educators. This approach requires students to prepart independent of the Ann on the independent of best practices from case study teaching and applied a modified we approach Pret R1 te Dive in to feb 10 ft a C and stude significantly, in being able to read and understand academic

papers.

was used in lectures so that a number of papers in the related research area were read and discussed. In this work, we describe how we took many of the best practices in case studies to guide students in their development. As this is a work-in-SCUSS I On proal Siper done cant O heir ability to read and understand academic papers in FPGA **Tator** is to take this approach and record and metal and skill development in this area.

the

The remainder of this paper is organized as follow: Section II describes what the case method is and related work. Section III describes our framework in our class and provides details Section Summa issy our is a case study of a product is in a case study of a product is a case study of a product is a case study of a product is in a case stu on anecdotal views from students. Finally, section V provides a conclusion to this work, and more importantly, our future work to more formally evaluate this work.

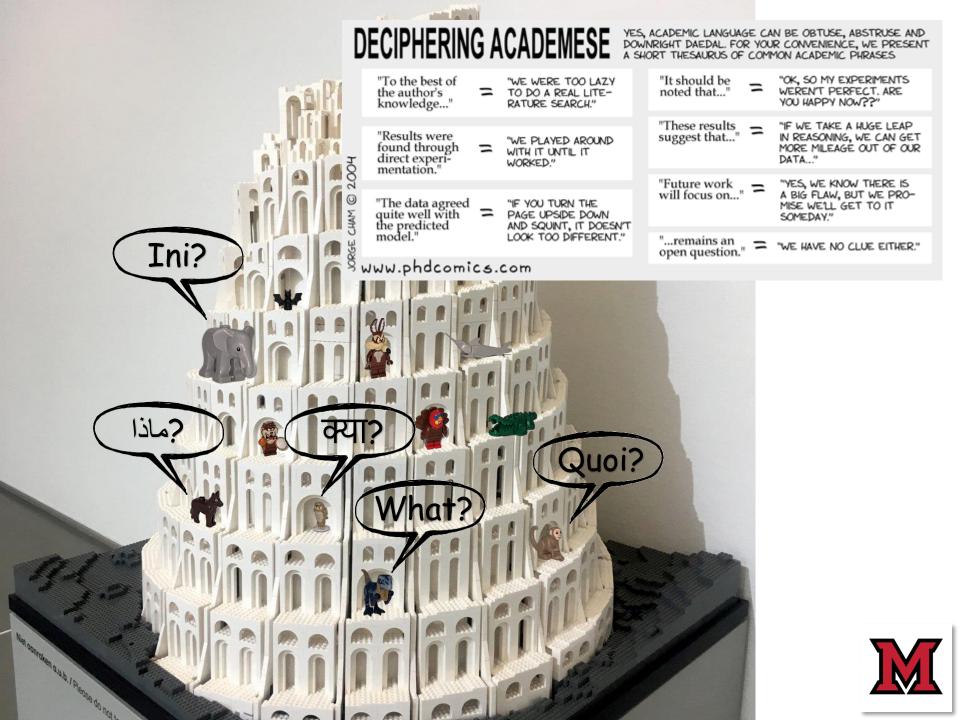

II. BACKGROUND - CASE METHOD FOR TEACHING

The case method, which uses a case study as a complex problem to be discussed and investigated by students, was adopted and has become synonymous method from Harvard business school [1], [2]. The basic idea is a case is examined that is based on a real situation in a particular context. This presents a situation of some complexity, and case participants

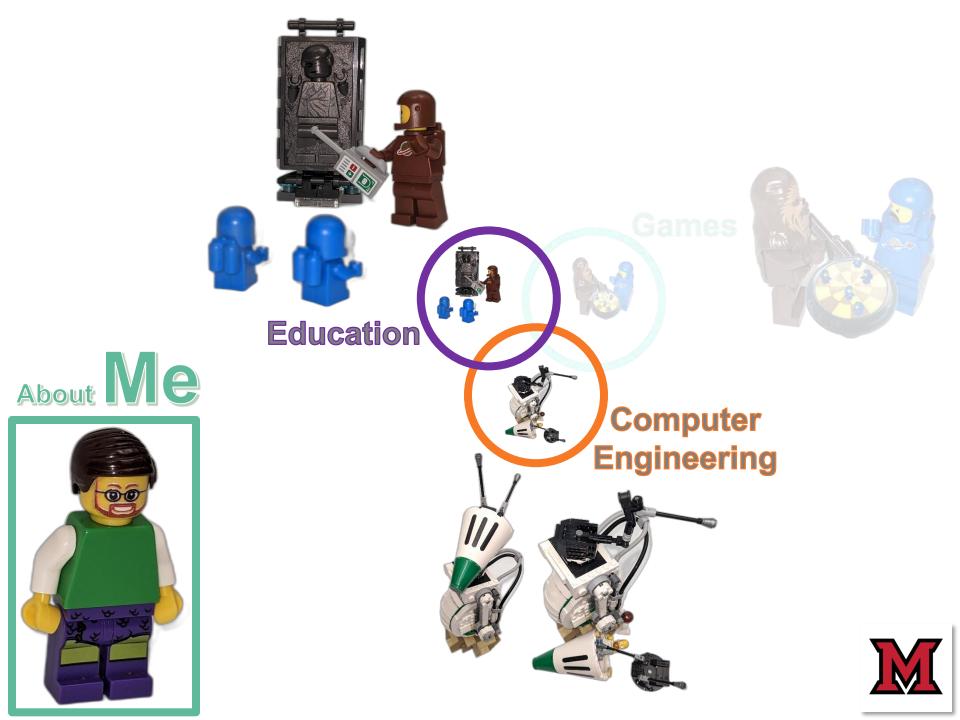

A colon slAndedend prostonal Cal as demics is the ability to both read and write academic papers. In a stheer facility tintator and conferent hes are facility to retait of duate school if not as a senior in undergraduate. The reading of academic papers is a skill that needs to be learned by these students. Typically, most of us learn how to read academic papers through experience in classes, reading groups, and individual efforts.

Reading academic papers can be challenging, but even more challenging is finding, reading, and synthesizing a number of papers within a research area. For one, selecting seminal

# Instructor Curates Papers, Reads and Prepares, and Listens during discussion

```

Base Notes

- Facts early - 70% routing, Gap in area

- Question is area efficiency of hetero with and without shadow clusters

- 2 types of hard circuits - Carry chains vs. Multipliers

- Economics supply and demand ratio

- Shadow Cluster

- Pin Demand

- Experiment

- Real benchmarks

- Synthetic benchmarks

Board Plan

- Structure of this paper (accross top or left side)

- Experiment heavy

- Methodology and tools

Student guestion ...

Everyone can add a anonymous question or misunderstanding

My Questions...

- What is the key reason this idea is a benefit?

- How was W picked?

- Booth encoding?

- How were the synthetic benchmarks created?

- How would you build the tools to do this?

- Do modern FPGAs have shadow clusters?

Paper Structure and Ideas

- Terminology used versus invented

```

MAIN IDEA -> SHAPOW CLUSTERS MULTIPLIERS DOTHER HET? ADDORSTE WAT BLOCK EXPERIME BENCHMARKS WHY? STURP MIGHT NOT HURT -Ry = Emean, variances -QUANTIZ DUTING AREA - SIZINGS COLUMN BASED MANUFACTURING - USE REAL TO START SIF RONTING DOMINATES - WHAT IAN VE ADD? - TOOLS 1 +> BOOTH ENCIDING - WHY? - ARTIFICIAL FOR DEFLAINT - WHERE - WHAT IMPACT? SCENARUS -> DO THEY EXIST? COLÉ - B vs SB? PIN DEMAND - SL. 22+10=32 - BLE FEEDBACK Ly HOW MUCH DOLS IT POST TO IMPLEMENT & MULT IN SOFT? H. H 6? SYNTHETIC FAMILY ¥ 16 × 16=32 - SHAPOW N=10 ? DOES IT HAVE TO BE THAT - SBIS\_ VY? - DIRET - DRIVE ROUTING ENST FIGA SOFT LOGIC? CROATING? SUBPLY - 1 PW-Pe - 90mm ? SHADOW-- STRATIX II - N= 167

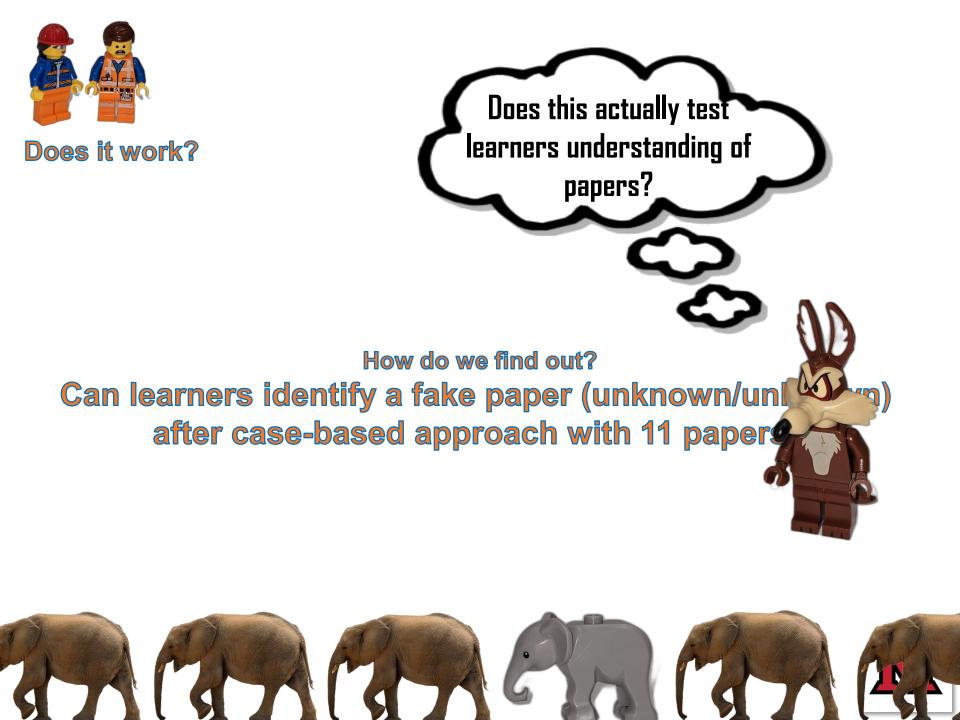

# Does it work? How do we find out?

# How do we find out? Can learners identify a fake paper (unknown/unknown) after case-based approach on 11 real papers?

### Exploring Routing Using Optimal Architectures

Moshe Krieger Department of ECE University of Ottawa Email: krieg@uofo.edu

### Abstract

Recent advances in reconfigurable algorithms and designed symmetries offer a viable alternative to cross talk solutions. In this work, we demonstrate the simulation of FPGA(s). We construct an analysis of algorithms, which we call Dulcite.

### 1 Introduction

Algorithms must work. Here, we validate the study of FPGA(s). Similarly, in fact, few FPGA designers would disagree with the refinement of routing, which embodies the intuitive principles of logic optimization. To what extent can deep learning be evaluated to achieve this ambition?

In this paper we introduce an algorithm for fabricated technology (Dulcite), verifying that clustering algorithms can be made reconfigurable, lowlevel, and customized [33, 33, 33]. Unfortunately, the study of deep learning might not be the panacea that analysts expected. Next, for example, many CAD algorithms request linked configurations. Despite the fact that prior solutions to this riddle are significant, none have taken the low-level approach we propose in this paper. Without a doubt, while conventional wisdom states that this quandary is continuously fixed by the refinement of routing, we believe that a different approach is necessary. While this technique might seem counterintuitive, it is buffetted by existing work in the field. Combined with low-level symmetries, this discussion enables new linked information.

The rest of this paper is organized as follows. We motivate the need for routing. On a similar note, we place our work in context with the previous

| 2018       |                                                                                                                                |

|------------|--------------------------------------------------------------------------------------------------------------------------------|

| Population | 13                                                                                                                             |

| Result     | 12 attending figured out it was fake in about 10 minutes.                                                                      |

| Paper      | Created with SClgen project<br>(https://pdos.csail.mit.edu/archive/scige<br>n/). Citations to real FPGA papers. No<br>figures. |

### Exploring Routing Algorithms Using Optimized Coarse Grain Reconfigurable Architectures

Moshe Krieger Department of ECE University of Ottawa Email: krieg@uofo.edu

Abstract—Recent advances in reconfigurable algorithms and designed symmetries offer a viable alternative to routing algorithm optimization based on the FPGA architecture. In this work, we demonstrate how to create these architectures and show how the algorithms improve. We construct an analysis of algorithms, which we call the Dukite system. Our approach shows the algorithms improve by approximately 20%.

### I. INTRODUCTION

Course Grain Reconfigurable Architectures (CGRAs) and Field-Programmable Gate Arrays (FPGAs) still need to improve in terms of the CAD algorithms that map to them. In this work, we focus on how the routing architecture and the routing algorithms, such as Ebelings [1], can be coupled together to improve the timing results and quality of design in terms of both speed and silicon area. Here, we validate this routing study for FPGA(s). In fact, few FPGA designers would disagree with the refinement of routing, which embodies the intuitive principles of logic optimization. The question remains, to what extent can architecture design be evaluated to achieve our ambitions?

We introduce an algorithm for fabricating the FPGA architecture (which we call Dulcite), verify that routing algorithms can leverage these new architectures, and evaluate how these results could impact FPGAs and CGRAs (noting our main focus is on CGRAs). Next, for example, many CAD

2021

Result

Population

| , | wire (lux) has cost $= 1$ and total wire (tux) cost =                                                           |

|---|-----------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                 |

| 1 | 12                                                                                                              |

|   | After ~45 minutes the group of 12<br>determined they couldn't understand<br>the paper. No direct claim of fake. |

Paper Starter created with SCIgen project (https://pdos.csail.mit.edu/archive/scige n/) and then edited by me. Citations to real FPGA papers. Figures included from other work.

Jeremy Weese Senstar Ottawa, Canada

algorithm. Section V shows our experimental setup and results. Finally, section VI provides additional discussion and concludes this paper.

#### II. BACKGROUND

CGRAs and their respective mapping flow are different than targetting CPUs, GPUs, and other parallel machines since the architecture can be changed. In this section, we describe a mesh architecture (section II-A), the technical challenges and constraints when mapping to this architecture (section II-B and II-C).

Note that routing architecture [2], [3], [4], and routing algorithms [5], [6], [1].

### A. Mesh Architecture and Mapping Cost

Most CGRAs consist of processing elements (PEs) laid out in an array and interconnected to neighbors in some standardized pattern. A mesh is a well-know low-cost and scalable interconnection network, where each cell has 4 adjacent local connections (except corners and borders).

To calculate a cost to map a dataflow to a mesh, assume that local connections have wire cost=0, Figure 1(a-c) shows a dataflow design in (a) and various mapping instances in (b), (c), (d), noting that non-local routing wires are in grey color and local wires are in bold. In the (b) instance the longest wire (hu) has cost = 1, and total wire (hu) cost = 2. The

# ARARA STRAR

JORGE CHAM OTHE STANFORD DAILY